この記事で言及する「ブートストラップ」は、電気(電子)回路の技法のそれであり、コンピュータの電源投入時やリセット時などの起動シーケンスのことではありません。

(回路技法の)ブートストラップとは

既にご存じの方は飛ばしてください。

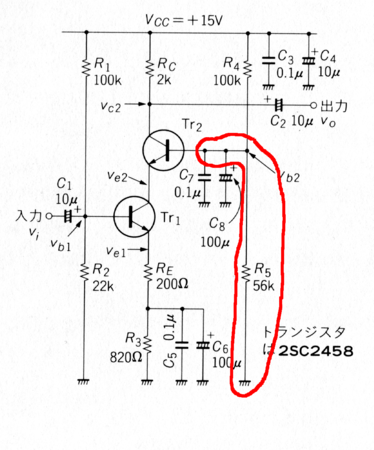

以下の2つの回路図は、『定本 トランジスタ回路の設計』(ISBN:9784789830485)の、第8章の 図2 と 図21 ですが、

赤い線で囲んだ部分に注目すると、1つめの回路ではグランド(0V)が基準となって動作する部分が、2つめの回路では自分自身の動作によって電位が決まる部分が基準になって動作するようになっています。

このように「自分自身の動作を利用して、動作電位が決まるような、電気(電子)回路の技法」は「ブートストラップ」と呼ばれています。語源はコンピュータの起動時の動作を指すそれとほぼ同じと思われますが、コンピュータのほうはプログラム内蔵方式のコンピュータができた戦後の頃にできた言葉であるのがほぼ確実であるのに対し、こちらはどうも戦時中(真空管回路)に、おそらくレーダーの研究開発などといったような秘密の下で考案されたものではないだろうかと思うのですが、由来を先日ざっと追ってみたものの、よくわかりませんでした。*1

最初に示した例はカスコード(cascode)方式の増幅回路のベース-エミッタ間の電位差を一定にするものでしたが、他に、ブートストラップの技法が使われる例としては、スイッチング電源のハイサイドがあります。

パワーMOSFETを電源などドライバ回路に使う場合、グランド側はNチャネルMOSFETを使えば、ゲート電圧が Vdd に近ければオン、グランド(Vss)に近ければオフ、という動作になるのでそれで良いわけですが、ハイサイド(電源側、Vdd 側)をそれと対称に構成しようとすると、PチャネルMOSFETが必要になります。しかし、Pチャネルは良い特性があまり得られず、品種も少ないですから、ハイサイドもNチャネルMOSFETで構成するわけですが、そうするとそのFETのソースの電位が Vdd に近くなっても十分に駆動するには、ゲートを駆動する電圧について Vdd + 2V~3V 程度のゲタを履かせる必要があります。

MOSFET のゲートですから、電流(電力)はたいして必要ないので、簡単なDCDCコンバータで電圧を作ったりするわけですが(『定本 続 トランジスタ回路の設計』の第10章に例があります)、スイッチング電源の場合は常に矩形波でパタパタしている電力を扱うわけですから、それをうまくキャパシタで利用してやる方法があります。

電源用モジュールの製品などで、外付け部品としてキャパシタが必要なものがありますが(ロームによるスイッチングレギュレータの解説 http://micro.rohm.com/jp/techweb/knowledge/dcdc/dcdc_sr/dcdc_sr01/829 や、TIによる降圧型スイッチングDCDCコンバータの解説 http://www.tij.co.jp/analog/jp/docs/analogsplash.tsp?contentId=54765 を参照)、そのキャパシタは「0V <=> Vdd」の矩形波を利用して「Vdd <=> Vdd+α」というような電圧を作ってやるのに使われているわけです。

1970年代のMOSプロセス

21世紀の現代ではもっぱらCMOSが使われているわけですが、1970年代~1980年代、なじみのある製品でいうと電卓戦争の時代から8~16ビットマイクロプロセッサの時代は、初期のメタル1層から2層へ、ロジックも PMOS → NMOS → CMOS と変遷があり、表向きにはスペックの向上として現れていますが、その裏にはいくつかのプロセスにおける変革があります(嶋さんによるこちらのコラム http://itpro.nikkeibp.co.jp/article/Watcher/20060323/233069/ が具体例に詳しい証言になっている)。

インテル4004(以下、ICの名前は単に4004等と呼ぶ)では、まだPMOSの時代で、しかもイオン注入によって部分的にディプリーション(ノーマリーオン)のMOSFETを作ることができるようになったのはもっと後であり(前述の嶋さんのコラムを参照。8080でもNMOSになっただけであり、イオン注入はZ80で採用された)*2、ブートストラップ方式によるちょっとしたトリックのような回路が使われています。

4004のブートストラップキャパシタ

4004では負電源とPMOSだったわけですが、それでは慣れない我々には少々非直感的なので、以下では正電源・NMOSで考えることにします。

相補型(CMOS)でないMOSで一般的な論理方式は ratioed logic と呼ばれるもので、NMOSの場合はハイサイドに小さめのトランジスタを置いて、プルアップする能動負荷とし、反対側に大きめのトランジスタでnotやnandやnorといった論理を作るものになります。

こんな感じです。上の能動負荷となっているFETについてですが、ディプリーション型であればゲートはソースかグランドに直結するわけですが、ここではエンハンスメント型ですから Vdd に直結されます。すると、出力が Low の時はロジック側の大きなトランジスタで引き下げられるわけですから問題ないわけですが、出力が High の時のプルアップが問題で、Low の時の電圧が上がりすぎないように小さめのトランジスタで駆動している上に、ゲート-ソース間の電圧として Vth 程度の電圧が必要ですから、Vdd まで出力を引き上げることができない、いわゆるフルスイングでない出力ということになってしまいます。

それでも問題ないように論理を工夫したりする方法もあるわけですが、4004では、以下で説明するようなちょっとトリックっぽいブートストラップの手法で、一時的に電源を越えるような電位を作って問題を回避しています。

4004の回路図は3枚に分かれていますが、そのうちの1枚「4004 ADDRESS REGISTER, INCREMENTER AND INDEX」というタイトルの図の片隅に、次のような注記があります。

ここで重要なのは下の2つで、プルアップ抵抗のように描かれているのは、実際にはMOSFETによる能動負荷だよ、ということを示すものです。上にあるほうは前述のような、単純にゲートをドレインに短絡したFETですが、トリックがあるのは下のFET2個とキャパシタを組み合わせたものです。「B」という記号は「ブートストラップ」の意でしょう。

この信号は時分割のバスなど、常に(矩形波による)オンオフがある信号であることが前提です。4004はレジスタに静的ではない回路を使っているため、動作をハードウェア的に完全に止めてしまうことはできない、完全には静的でない論理回路ですが、(実は)この部分も完全に静的ではなくある程度の動作が常に必要です。

まず、出力が Low で定常的だとする所から始めます。上のFETにより下のFETのゲートは Vdd-Vth 程度の電位になっています。出力は Low で、下のFETのゲート-ソース間電圧は十分にありますから、下のFETもオンになっていますが、前述のように ratioed logic のためにロジック側で出力は Low に引き下げられている、というような状態になっています。キャパシタがあるわけですが、ICの中に作れる程度ですから、定常状態で放置されれば電荷はそう長くは保ちません。

次に、ロジックの入力が変化して、出力が High に変化し始めた、とします。するとキャパシタが、いわゆる「スピードアップコンデンサ」のそれと似たような働きをすることになって、上のFETのソース=下のFETのゲートの電位が、出力電圧の変化に合わせて上がってゆき、2*Vdd-Vth 程度まで上がることになります。これにより下のFETがオンに保たれるため、普通であれば Vdd まで上がらないはずの出力が、Vdd まで上がります。

また、上のFETはゲート電圧よりもソース電圧のほうが高いため、オフ状態になります。

(普通のディスクリートのMOSFETで似たような回路を作ろうとした場合、ソース電極がサブストレート(バルク)にも接続されていて寄生ダイオードが存在するため(よく使われる右のような記号はそれを表現したものです)、ソースの電位をドレインより上げても電荷が抜けていってしまいますが、ICの中ではソースとサブストレートを別にすることができます)

以上のようにして、4004ではブートストラップの手法により、動的な一部の信号線の( High への)駆動力が強化されています。

実装

マスクパターンでは、以上で説明したキャパシタが、余計な面積を必要としないように巧妙に形成されているはずです(が、力不足で説明できる所まで理解できていません)。

文献

嶋さんの本、

- 作者: 嶋正利

- 出版社/メーカー: 岩波書店

- 発売日: 1987/08/28

- メディア: 単行本

- クリック: 11回

- この商品を含むブログ (14件) を見る

には、この手法に関して直接的な言及はありません。嶋さんは4004チップに関して論理設計だけでなく回路やマスクの作業もやっておられますから、それ自体については承知のはずですが、おそらく、フェデリコ・ファジンさんの功績であることから(自分のそれと混同されることを避けるために)言及しなかったのかもしれません。Z80においてイオン注入法を採用したことで、ディプリーション負荷FETが使えるようになった、という間接的言及といえる記述はあります(イオン注入法がデッドコピー対策のトラップのためにも使われた、という記述も興味深い所です)。

近年出たドキュメンタリー、

- 作者: マイケルマローン,Michael S. Malone,土方奈美

- 出版社/メーカー: 文藝春秋

- 発売日: 2015/09/12

- メディア: 単行本

- この商品を含むブログを見る

には、次のような記述があります( p. 183 )。

このなかでいわば「副産物」*3のように生まれた発明が、やがて半導体史上シリコンゲートと並ぶ意義を持つことになった。ファジンは個々のゲートを、相方となるトランジスタの上側にブートストラップしたのだ。それまで不可能と思われていたことである。この手法はすぐに普及し、それから四〇年にわたってほぼすべての種類のチップに利用された。(この段落後略)

というようにあるのですが、ここまでで説明したように4004で使われたブートストラップは、イオン注入法によるディプリーション負荷FETが使えるようになるまでの「つなぎ」的な色の濃い手法であり、CMOSになってからは忘れられたような手法ではないかと思いますので、何か違う感じもします。もしかしたら翻訳の際の影響かもしれませんが、もうひとつの鍵となった技術である buried contact が関係あるかもしれません。

なお同書は、(『電子立国』ではあまり語られなかったため、日本などではあまり知られていない)当時の、また他の多くの時代のインテルの内情が書かれており、「マイクロプロセッサは誰の功績か」などといった話題についても(他社への言及が無い点を除けば)フェアかつ背景に踏み込んだ記述もあり、必読の1冊ではないかと思います。

参考リンク

*1:1955年に出願された特許の中に出てくるのが確認できるのだが、あたりまえの技術として言及されているように見える https://www.google.com/patents/US2850629 。

*2:4004の回路の素子について、デプレッション型、と言及している記事があるが http://www.atmarkit.co.jp/fsys/zunouhoudan/139zunou/4004_40thanv.html 誤解ではないかと思われる。

*3:原文では傍点